# MUFFAKHAM JAH COLLEGE OF ENGINEERING AND TECHNOLOGY

## PC451EC ANALOG ELECTRONIC CIRCUITS LAB

(With effect from the academic year 2015-2016)

## STUDENT'S MANUAL

## **DEPARTMENT OF**

## ELECTRONICS AND COMMUNICATION ENGINEERING

## Vision and Mission of the Institution

## Vision

To be part of universal human quest for development and progress by contributing high calibre, ethical and socially responsible engineers who meet the global challenge of building modern society in harmony with nature.

## Mission

- To attain excellence in imparting technical education from the undergraduate through doctorate levels by adopting coherent and judiciously coordinated curricular and co-curricular programs

- To foster partnership with industry and government agencies through collaborative research and consultancy

- To nurture and strengthen auxiliary soft skills for overall development and improved employability in a multi-cultural work space

- To develop scientific temper and spirit of enquiry in order to harness the latent innovative talents

- To develop constructive attitude in students towards the task of nation building and empower them to become future leaders

- To nourish the entrepreneurial instincts of the students and hone their business acumen.

- To involve the students and the faculty in solving local community problems through economical and sustainable solutions.

## **Vision and Mission of ECE Department**

## Vision

To be recognized as a premier education center providing state of art education and facilitating research and innovation in the field of Electronics and Communication.

## Mission

We are dedicated to providing high quality, holistic education in Electronics and Communication Engineering that prepares the students for successful pursuit of higher education and challenging careers in research, R& D and Academics.

## **Program Educational Objectives of B. E (ECE) Program:**

- 1. Graduates will demonstrate technical competence in their chosen fields of employment by identifying, formulating, analyzing and providing engineering solutions using current techniques and tools

- 2. Graduates will communicate effectively as individuals or team members and demonstrate leadership skills to be successful in the local and global cross-cultural working environment

- 3. Graduates will demonstrate lifelong learning through continuing education and professional development

- 4. Graduates will be successful in providing viable and sustainable solutions within societal, professional, environmental and ethical contexts

MUFFAKHAM JAH COLLEGE OF ENGINEERING AND TECHNOLOGY

## BANJARA HILLS, ROAD NO-3, TELANGANA

LABORATORY MANUAL

## FOR

## ANALOG ELECTRONIC CIRCUITS LAB

**Prepared by:**

Checked by:

Approved by:

## MUFFAKHAM JAH COLLEGE OF ENGINEERING AND TECHNOLOGY

## DEPARTMENT OF ELECTRONICS AND COMMUNICATIONS ENGINEERING

## (Name of the Subject/Lab Course): Analog Electronic Circuits

| Code: EC281                                       | Programme: UG              |

|---------------------------------------------------|----------------------------|

| Branch: ECE                                       | Version No: 1              |

| Year : II                                         | <b>Updated on: 20/3/16</b> |

| Semester :II                                      | No. of Pages:              |

| Classification Status(Unrestricted/restricted): U | Unrestricted               |

| Distribution List :Department, Lab, Library, L    | ab Incharge                |

| Prepared by: 1) Name :                            | 1) Name :                  |

| 2) Sign :                                         | 2) Sign :                  |

| <b>3)Designation :</b>                            | 3) Designation :           |

| 4) Date :                                         | 4) Date :                  |

| Verified by: 1) Name :                            | * For Q.C Only             |

| 2) Sign :                                         | 1) Name :                  |

| 3)Designation :                                   | 2) Sign :                  |

| 4) Date :                                         | 3) Designation :           |

|                                                   | 4) Date :                  |

| Approved by: (HOD) 1) Name:                       |                            |

| 2) Sign :                                         |                            |

|                                                   |                            |

3) Date :

EC 281

## ANALOG ELECTRONIC CIRCUITS LAB

Instructions Duration of University Examination University Examination Sessionals **Objectives:**  3 Periods per week 3 Hours 50 Marks 25 Marks

- 1. Verify frequency response of BJT and FET amplifiers

- 2. Design different negative feedback amplifiers circuits

- 3. Design AF and RF oscillator circuits.

- 4. Design power amplifiers

- 5. Demonstrate various circuits using PSPICE and verifying functionality.

- 6. Design passive filters.

#### Lab Experiments:

## PART – A

- 1. Design & frequency response of single stage and multistage RC Coupled amplifier using BJT.

- 2. Design & frequency response of single stage and multistage RC Coupled amplifier using FET.

- 3. Voltage series feedback amplifier.

- 4. Current shunt feedback amplifier.

- 5. Voltage shunt feedback amplifier.

- 6. Current series feedback amplifier.

- 7. RC phase shift, Wein bridge oscillator.

- 8. Hartley oscillator & Colpitts Oscillator.

- 9. Design of Class-A power amplifier.

- 10. Design of Class-B power amplifier.

- 11. Frequency response of Tuned Amplifiers (Single and Double).

- 12. Transistor regulator.

- 13. SPICE Simulation and analysis of BJT and FET amplifier circuits.

#### PART – B

14. Constant K low pass and high pass filter

15. m-derived low pass and high pass filter

#### **Suggested Reading:**

- 1. Paul B. Zbar, Albert P.Malvino, Michael Miller, *Basic Electronics, A Text- Lab Manual*,7<sup>th</sup> ed., McGraw Hill Education (India) Private Limited,2001.

- 2. David Bell A, Laboratory Manual for Electrical Circuits, PHI-New Delhi, 2009.

- 3. Hayt W H Kemmerly J.E and Durbin SM, *Engineering Circuit Analysis*, 8<sup>th</sup> ed., McGraw Hill Education (India) Private Limited, 2013.

Note:

- 1. A total of not less than 12 experiments must be carried out during the semester. (Where ever possible, more than 1 lab experiment should be carried out in one lab session of 3 periods per week.)

- 2. The experiments should be performed on bread board using discrete components.

- 3. There should not be more than 2 students per batch while performing any of the lab experiment.

## ANALOG ELECTRONICS AND INTEGRATED CIRCUITS LAB

## GENERAL GUIDELINES AND SAFETY INSTRUCTIONS

- 1. Sign in the log register as soon as you enter the lab and strictly observe your lab timings.

- 2. Strictly follow the written and verbal instructions given by the teacher / Lab Instructor. If you do not understand the instructions, the handouts and the procedures, ask the instructor or teacher.

- 3. Never work alone! You should be accompanied by your laboratory partner and / or the instructors / teaching assistants all the time.

- 4. It is mandatory to come to lab in a formal dress and wear your ID cards.

- 5. Do not wear loose-fitting clothing or jewellery in the lab. Rings and necklaces are usual excellent conductors of electricity.

- 6. Mobile phones should be switched off in the lab. Keep bags in the bag rack.

- 7. Keep the labs clean at all times, no food and drinks allowed inside the lab.

- 8. Intentional misconduct will lead to expulsion from the lab.

- 9. Do not handle any equipment without reading the safety instructions. Read the handout and procedures in the Lab Manual before starting the experiments.

- 10. Do your wiring, setup, and a careful circuit checkout before applying power. Do not make circuit changes or perform any wiring when power is on.

- 11. Avoid contact with energized electrical circuits.

- 12. Do not insert connectors forcefully into the sockets.

- 13. **NEVER** try to experiment with the power from the wall plug.

- 14. Immediately report dangerous or exceptional conditions to the Lab instructor / teacher: Equipment that is not working as expected, wires or connectors are broken, the equipment that smells or "smokes". If you are not sure what the problem is or what's going on, switch off the Emergency shutdown.

- 15. Never use damaged instruments, wires or connectors. Hand over these parts to the Lab instructor/Teacher.

- 16. Be sure of location of fire extinguishers and first aid kits in the laboratory.

- 17. After completion of Experiment, return the bread board, trainer kits, wires, CRO probes and other components to lab staff. Do not take any item from the lab without permission.

- 18. Observation book and lab record should be carried to each lab. Readings of current lab experiment are to be entered in Observation book and previous lab experiment should be written in Lab record book. Both the books should be corrected by the faculty in each lab.

- 19. Handling of Semiconductor Components:Sensitive electronic circuits and electronic components have to be handled with great care. The inappropriate handling of electronic component can damage or destroy the devices. The devices can be destroyed by driving to high currents through the device, by overheating the device, by mixing up the polarity, or by electrostatic discharge (ESD). Therefore, always handle the electronic devices as indicated by the handout, the specifications in the data sheet or other documentation.

- 20. Special Precautions during soldering practice

- a. Hold the soldering iron away from your body. Don't point the iron towards you.

- b. Don't use a spread solder on the board as it may cause short circuit.

- c. Do not overheat the components as excess heat may damage the components/board.

- d. In case of burn or injury seek first aid available in the lab or at the college dispensary

## List of Experiments

## Page

| 1) Single Stage R-C Coupled CE BJT Amplifier  | 08 |

|-----------------------------------------------|----|

| 2) Single Stage R-C Coupled CS JFET Amplifier | 13 |

| 3) Two Stage R-C Coupled CE BJT Amplifier     | 17 |

| 4) Two Stage R-C Coupled CS FET Amplifier     |    |

| 5) Voltage Series Feedback Amplifier          | 27 |

| 6) Current Shunt Feedback Amplifier           |    |

| 7) RC Phase-Shift Oscillator                  |    |

| 8) Colpitts Oscillator                        |    |

| 9) Hartley Oscillator                         | 42 |

| 10) Single Tuned Amplifier                    | 45 |

| 11) Double Tuned Amplifier                    | 49 |

| 12) Constant K Low Pass Filter                | 53 |

| 13) m-Derived High Pass Filter                | 56 |

| 14)Appendix                                   | 59 |

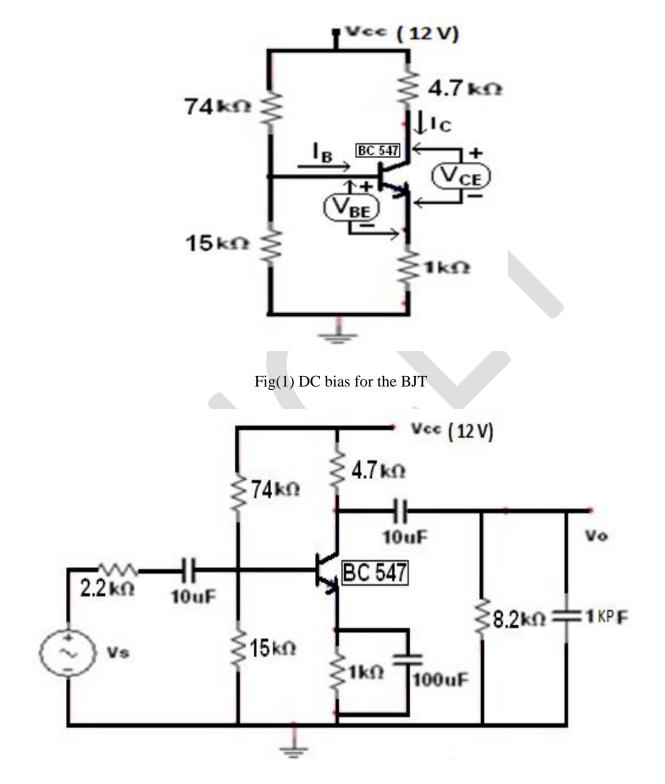

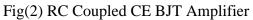

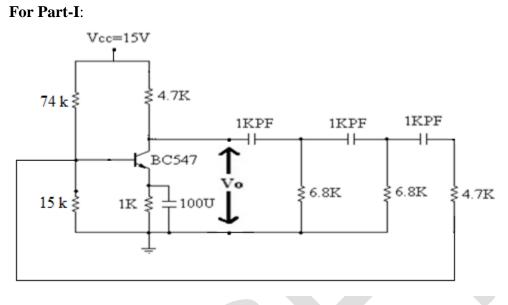

## **EXPERIMENT NO: 1**

## SINGLE STAGE R-C COUPLED CE BJT AMPLIFIER

#### Aim:-

- 1. To design a single stage R-C coupled Common Emitter BJT amplifier and plot its frequency response.

- 2. To calculate the gain and find the cut off frequencies and Bandwidth.

### **Components:**

| Name                                                                                               | Quantity    |

|----------------------------------------------------------------------------------------------------|-------------|

| Transistor BC547                                                                                   | 1           |

| Resistor 74K $\Omega$ , 15K $\Omega$ , 4.7K $\Omega$ , 1K $\Omega$ , 2.2K $\Omega$ , 8.2K $\Omega$ | 1,1,1,1,1,1 |

| Capacitor 10µF,100µF, 1 KPF                                                                        | 2, 1,1      |

### **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

### **Specifications:**

### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>0</sup>C

- $h_{fe} = 110 220$

## **Theory:**

An amplifier is an electronic circuit that can increase the strength of a weak input signal without distorting its shape. A BJT can be used as an amplifier in the active region. The factor by which the input signal gets multiplied after passing through the amplifier circuit is called the gain of the amplifier. It is given by the ratio of the output and input signals.

## Gain = output signal / input signal

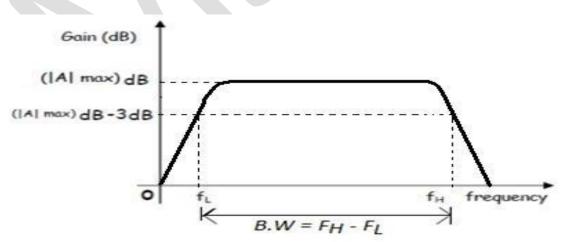

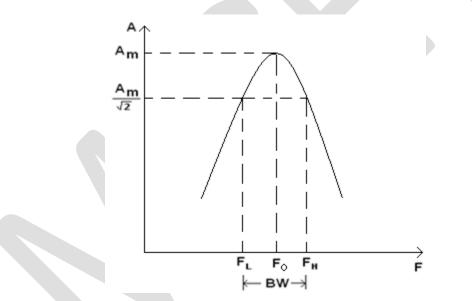

A self bias circuit is used in the amplifier circuit because it provides highest Q-point stability among all the biasing circuits ie, its stability factor is the least of all. A plot of the gain of the amplifier and frequency is called the frequency response curve. The frequencies at which the gain of the amplifier is  $1/\sqrt{2}$  times the maximum value of gain are called the cutoff frequencies or 3 dB frequencies. The difference of these cutoff frequencies is called the bandwidth of the amplifier.

$$Bandwidth = f_H - f_L$$

Where  $f_L$  is called the lower cutoff frequency and  $f_H$  is called the higher cutoff frequency.

## **Design:**

Q: Design a single stage RC coupled amplifier using a BJT in CE configuration to provide a gain of 100, lower cutoff frequency 55 Hz and an upper cutoff frequency of 55 KHz. Use BJT BC547 for which  $\beta = 200$ ,  $h_{fe} = 50$ ,  $h_{ie} = 1.5 \text{ K}\Omega$  and  $V_{BE(active)} = 0.65\text{V}$ . The biasing conditions are as follows. $V_{CC} = 12\text{V}$ ,  $I_C = 1\text{mA}$ ,  $V_{CE} = 6\text{V}$  and Stability factor is S = 10. Use  $R_C = 4.7\text{K}\Omega$ .

## <u>Solution:</u>

Use,  $I_C = \beta \times I_B$

$\Rightarrow I_{R} = 5\mu A$

Apply KVL to the output loop:

$-V_{CC} + I_C \times R_C + V_{CE} + I_C \times R_E = 0$  $\Rightarrow R_E = 1.3K\Omega$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

And  $R_B = \frac{R_1 \times R_2}{R_1 + R_2}$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1+\beta}{1+\frac{\beta \times R_E}{R_B + R_E}}$$

$$\Rightarrow R_B = 12.31K\Omega$$

Apply KVL to the input loop, then

$$-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$$

$$\implies V_B = 2.01 \,\mathrm{V}$$

Divide  $R_B$  with  $V_B$ :

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_B} = 73.5 K\Omega$$

Also,

$$R_B = \frac{R_1 \times R_2}{R_1 + R_2} \implies R_2 = 14.8K\Omega$$

Design of R<sub>L</sub>:-

We know that, gain

$$A_V = \frac{-h_{fe} \times R_L}{h_{ie}}$$

$\Rightarrow R_L = 3K\Omega$

But,

$$R_L^{'} = \frac{R_L \times R_C}{R_L + R_C}$$

$\Rightarrow R_L = 8.3K\Omega$ Design of C<sub>E</sub> and C<sub>sh</sub>:-

We know that

$$f_L = \frac{1 + n_{fe}}{2\pi h_{ie} C_E}$$

$$\Rightarrow C_E = 100 \mu F$$

-

Also,

$$f_H = \frac{1}{2\pi R_L C_{sh}} \implies C_{sh} = 1KPF$$

Assume,  $C_b = C_c = 10 \mu F$  and  $R_S = 2.2 K \Omega$

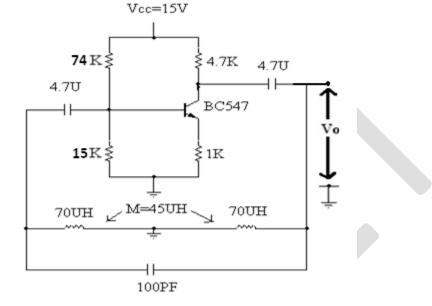

## Circuit diagram:

## Procedure:

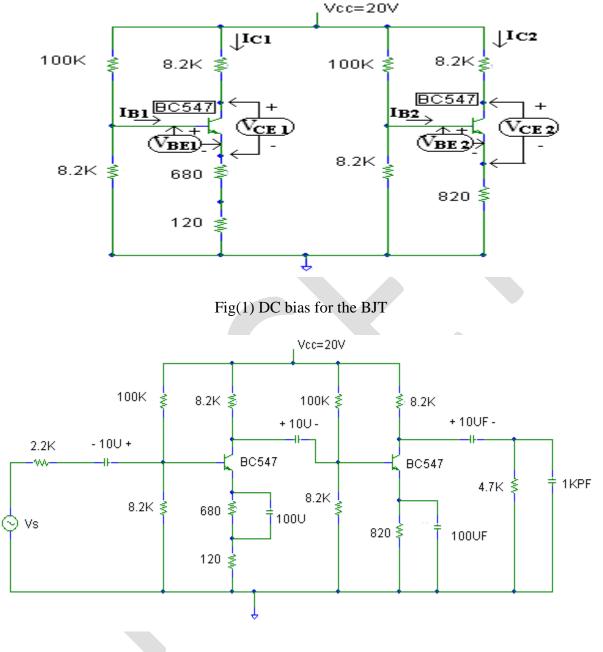

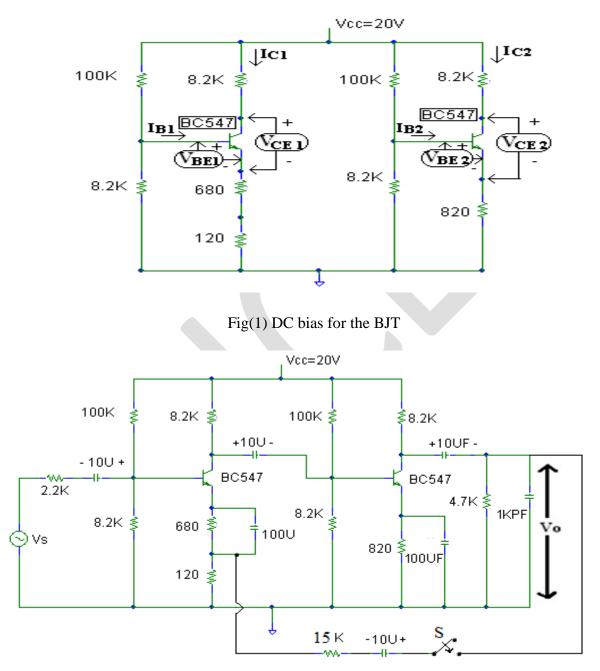

1. Connect the circuit as shown in fig 1 and obtain the DC bias conditions  $V_{BE}$ ,  $I_B$ ,  $V_{CE}$ ,  $I_C$ .

$V_{CE}$  = .....

I<sub>C</sub> = .....

- 2. Connect the circuit as shown in fig 2, Set source voltage as 30mV P-P at 1 KHz frequency using the function generator.

- 3. Keeping the input voltage as constant, vary the frequency from 30 Hz to 1 MHz in regular steps and note down the corresponding output P-P voltage.

- 4. Plot the graph for gain in (dB) verses Frequency on a semi log graph sheet.

- 5. Calculate the bandwidth from the graph.

## **Observations:**

$V_S = 30mV$

DC conditions:

$I_B = \dots$

Frequency Response:

| Frequency | Vs (Volts) | Vo(Volts) | Gain = Vo/Vs | Gain(dB) = 20 log(Vo/Vs) |

|-----------|------------|-----------|--------------|--------------------------|

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

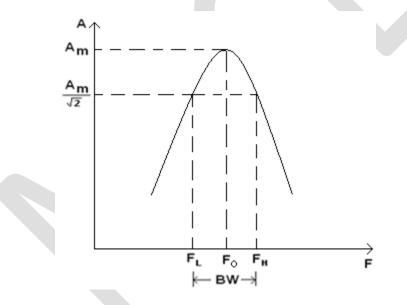

## Expected graph:

Fig(3) frequency response of RC Coupled CE BJT Amplifier

## AEC LAB MANUAL

## **Result:**

- 1. The frequency response curve of the amplifier is plotted.

- Mid band gain, A<sub>m</sub> = .....

Lower cutoff frequency, f<sub>L</sub> = .....

- Higher cutoff frequency,  $f_H = \dots$

Bandwidth  $= f_H - f_L = \dots$

## **EXPERIMENT NO: 2**

### SINGLE STAGE R-C COUPLED CS JFET AMPLIFIER

#### Aim:

- 1. To design a single stage R-C coupled Common Source JFET amplifier and plot its frequency response.

- 2. To find the cut off frequencies, Bandwidth and calculate its gain.

#### **Components:**

| Name                                                              | Quantity   |

|-------------------------------------------------------------------|------------|

| JFET BFW 11                                                       | 1          |

| Resistor 4.7K $\Omega$ , 27K $\Omega$ , 1K $\Omega$ , 1M $\Omega$ | 1, 1, 1, 1 |

| Capacitor 1µF, 10µF, 1KPF                                         | 2,1,1      |

### **Equipment:**

| Name               | Range     | Quantity |

|--------------------|-----------|----------|

| Bread Board        |           | 1        |

| Dual power supply  | 0-30V     | 1        |

| CRO                | (0-20)MHz | 1        |

| Function Generator | (0-1)MHz  | 1        |

| Connecting Wires   |           |          |

### **Specifications:**

### For FET BFW11:

Gate Source Voltage  $V_{GS} = -30V$

Forward Gain Current  $I_{GF} = 10mA$

Maximum Power Dissipation  $P_D = 300 \text{mW}$

### Theory:

An amplifier is an electronic circuit that can increase the strength of a weak input signal without distorting its shape. A JFET can be used as an amplifier in the pinch-off region. The factor by which the input signal gets multiplied after passing through the amplifier circuit is called the gain of the amplifier. It is given by the ratio of the output and input signals.

Gain = output signal / input signal

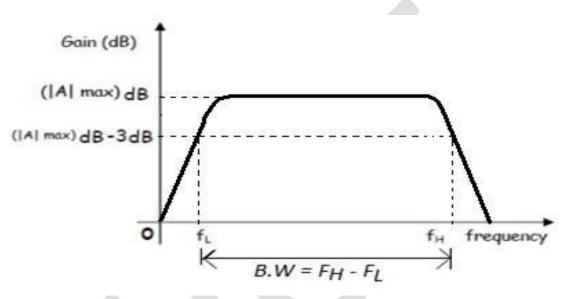

A source self bias circuit is used in the amplifier circuit. A plot of the gain of the amplifier and frequency is called the frequency response curve. The frequencies at which the gain of the amplifier is  $1/\sqrt{2}$  times the maximum value of gain are called the cutoff frequencies or 3 dB frequencies. The difference of these cutoff frequencies is called the bandwidth of the amplifier.

### **Bandwidth** = $f_H - f_L$

Where  $\mathbf{f}_{\mathbf{L}}$  is called the lower cutoff frequency and  $\mathbf{f}_{\mathbf{H}}$  is called the higher cutoff frequency.

This amplifier is commonly used in buffering applications where the demand is for higher input impedance and gain is not of prime importance.

#### **Design:**

Q: Design a single stage JFET amplifier to provide a voltage gain of 10, lower cutoff frequency 50 Hz and an upper cutoff frequency of 50 KHz. Use JFET BFW10 for which  $I_{DSS} = 13mA$ ,  $V_P = -4V$ ,  $g_m = 3mS$ , and  $r_d = 20K\Omega$ . The biasing conditions are as follows.  $V_{DD} = 25V$ ,  $V_{DS} = 10V$ ,  $I_D = 2.5mA$ .

Solution:

Using

$$I_D = I_{DSS} \times \left(1 - \frac{V_{GS}}{V_P}\right)^2$$

$$\Rightarrow V_{GS} = V_P \times \left(1 - \sqrt{\frac{I_D}{I_{DSS}}}\right) = -2.25V$$

Assume that  $R_g = 1M\Omega$ Apply KVL to input loop:

$$-I_G \times R_g + V_{GS} + I_D \times R_S = 0$$

But  $I_G = 0$ .

$$\Rightarrow R_{S} = \frac{-V_{GS}}{I_{D}} = 0.9K\Omega \cong 1K\Omega$$

$-V_{DD} + I_D \times R_D + V_{DS} + I_D \times R_S = 0$  $\implies R_D = 5K\Omega \cong 4.7K\Omega$

We know that the voltage gain of a FET amplifier is given by,

$$A_{V} = -g_{m} \left( \frac{r_{d} \times R_{L}^{'}}{r_{d} + R_{L}^{'}} \right) \Longrightarrow R_{L} = 27 K\Omega$$

To find C<sub>s</sub>:

$$C_s = \frac{g_m}{2\pi f_L} = 10\,\mu F$$

To find C<sub>Sh</sub>:

$$C_{Sh} = \frac{1}{2\pi R_L^{"} f_H} = 1nF = 1KPF$$

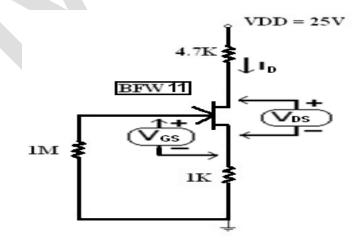

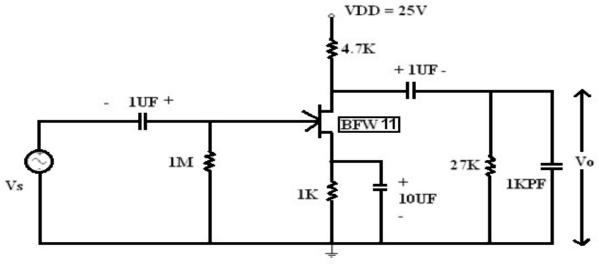

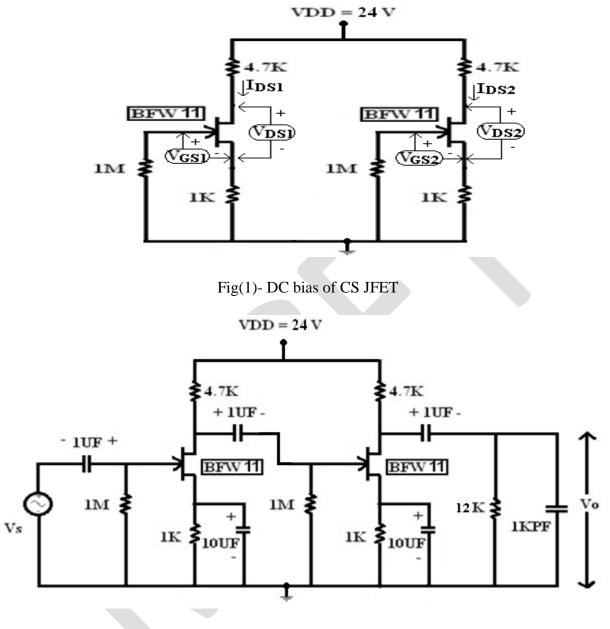

Apply KVL to the output loop: **Circuit diagram:**

Fig(1)- DC bias of CS JFET

**RC-Coupled CS JFET Amplifier**

Fig(2)- RC Coupled CS JFET Amplifier

## Procedure:

- 1. Connect the circuit as shown in fig 1 and obtain the DC bias conditions  $V_{GS}$ ,  $I_G$ ,  $V_{DS}$ ,  $I_D$ .

- 2. Connect the circuit as shown in fig 2, Set source voltage as 50mV P-P at 1 KHz frequency using the function generator.

- 3. Keeping the input voltage as constant, vary the frequency from 30 Hz to 1 MHz in regular steps and note down the corresponding output P-P voltage.

- 4. Plot the graph for gain in (dB) verses Frequency on a semi log graph sheet.

- 5. Calculate the bandwidth from the graph.

### **Observations:**

$V_S = 50mV$

DC conditions:-

$V_{GS} = \dots$

$V_{DS} = \dots$

$I_G = \dots$

| T —     |  |   |  |  |  |  |  |  |  |   |   |  |

|---------|--|---|--|--|--|--|--|--|--|---|---|--|

| $I_D =$ |  | • |  |  |  |  |  |  |  | • | • |  |

## AEC LAB MANUAL

## Frequency Response:

| Frequency | Vs (Volts) | Vo(Volts) | Gain = Vo/Vs | Gain(dB) = 20 log(Vo/Vs) |

|-----------|------------|-----------|--------------|--------------------------|

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

|           |            |           |              |                          |

**Expected graph:**

Fig(3)- Frequency response of RC Coupled CS JFET Amplifier

## **Result:**

- 1. The frequency response curve of the amplifier is plotted.

- 2. Mid band gain, $A_m = \dots$ 3. Lower cutoff frequency, $f_L = \dots$ Higher cutoff frequency, $f_H = \dots$ Bandwidth, $f_H f_L = \dots$

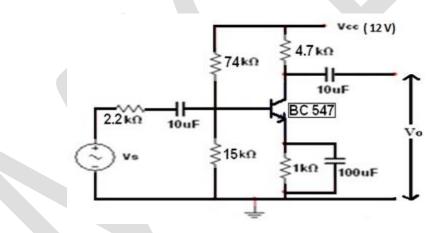

## **EXPERIMENT NO: 3**

## TWO STAGE R-C COUPLED CE BJT AMPLIFIER

#### Aim:-

- 1. To design a two stage R-C coupled Common Emitter BJT amplifier and plot its frequency response.

- 2. To see the effect of cascading upon gain and bandwidth,

#### **Components:**

| Name                                                                                                                                                      | Quantity      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Transistor BC547                                                                                                                                          | 2             |

| Resistor $100 \mathrm{K}\Omega$ , $8.2 \mathrm{K}\Omega$ , $820 \Omega$ , $680 \Omega$ , $120 \Omega$ , $4.7 \mathrm{K}\Omega$ , $2.2 \mathrm{K}\Omega$ , | 2,4,1,1,1,1,1 |

| Capacitor 10µF,100µF, 1 KPF                                                                                                                               | 3, 2,1        |

### **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

## **Specifications:**

### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

### **Theory:**

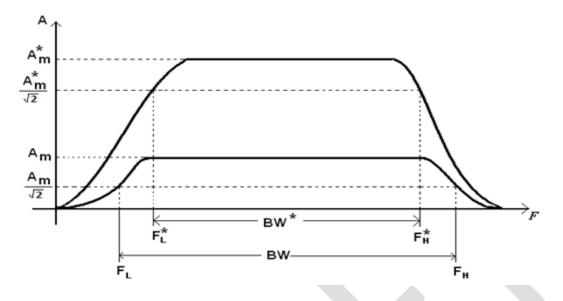

Cascading in amplifiers is a process of connecting the output of one amplifier to the input of the next and so on so forth. Cascading is used to increase the gain of the amplifier, but due to cascading bandwidth gets reduced.

In a multistage amplifier the overall voltage gain is the product of individual voltage gains. But the bandwidth of a multistage amplifier is always smaller than the bandwidth of individual stages.

## Design:

Design a two stage amplifier to provide an overall mid band gain of 900, and a bandwidth of 55 KHz. Use BJT BC547 for which  $\beta = 250$ ,  $h_{fe} = 60$ ,  $h_{ie} = 1.5 K\Omega$  and  $V_{BE(active)} = 0.65$  V. The biasing conditions are  $V_{CC} = 20V$ ,  $I_C = 1mA$ ,  $V_{CE} = 11V$  and stability factor S = 10. Use  $R_C = 8.2K$ ,  $R_S = 2.2K$  and  $C_b = C_c = 10\mu$ F.

by

Design:-

Apply KVL to output loop:

$$-V_{CC} + I_C \times R_C + V_{CE} + I_C \times R_e = 0$$

$\Rightarrow R_e = 800\Omega$

We know that the stability factor is given

$S = \frac{1 + \beta}{1 + \frac{\beta \times R_e}{R_b + R_e}} \Rightarrow R_b = 7.69K\Omega$

Applying KVL to the input loop:

Applying KVL to the input loop:

$$-V_b + I_B \times R_b + V_{BE} - I_E \times R_e = 0$$

$\Rightarrow V_b = 1.5V$

$R_1 = \frac{V_{CC} \times R_b}{V_b} \cong 100 K\Omega$ Now,

Also,

$$R_b = \frac{R_1 \times R_2}{R_1 + R_2} \implies R_2 = 8.2K\Omega$$

**Design of R\_L:** To reduce the gain of first stage, split its emitter resistance into two resistors and leave one resistor un-bypassed. Assume that a gain of 7.5 is desired from the first stage. Also, the load resistor for this stage is a parallel combination of  $R_{C1}$ ,  $R_{B2}$  and  $R_{i2}$ , which is equal to 1.08K $\Omega$ .

Then,

$$\Rightarrow R_{e1} = 120\Omega$$

$A_{V1} = \frac{-h_{fe} \times R_{L1}}{h_{ie} + (1 + h_{fe}) \times R_{e1}}$

But,  $R_{e1} = R_{e1} + R_{e1}^{"}$  $\Rightarrow R_{e1} = 700\Omega \cong 680\Omega$

An overall gain of 900 is desired from the amplifier of which 7.5 is provided by first stage. Therefore the second stage must provide a gain of 120.

We know that,

$$A_{V2} = \frac{-h_{fe} \times R_{L2}^{'}}{h_{ie}} \Longrightarrow R_{L2}^{'} = 3K\Omega$$

$$R_{L2}^{'} = \frac{R_{C2} \times R_{L2}}{R_{C2} + R_{L2}} \Longrightarrow R_{L2} = 4.7K\Omega$$

But,

Overall bandwidth is given as 55 KHz. As the shunt capacitor is placed in the second stage, the bandwidth for first stage will be very high in comparison with that for the second stage. Therefore the overall bandwidth will be equal to the bandwidth of the second stage.

$$\therefore (BW) = (BW)_2 \cong f_{H2} = 55KHz$$

Now,

$$C_{sh} = \frac{1}{2\pi R_{L2}^{"} f_{H2}} = 1nF = 1KPF$$

Assume the emitter bypass capacitor to be  $100\mu$ F for each stage.

## Circuit diagram:

Fig(2) Two stage RC Coupled CE BJT Amplifier

## **Procedure:**

- 1) Connect the circuit as shown in figure 1.

- 2) Note the DC conditions i.e, the values of base, collector currents and base to emitter, collector to emitter voltages for each stage.

3) Connect the circuit as shown in figure 2, Adjust the input signal frequency to 1 KHz and the peak to peak value of  $V_{i1}$  to 2 or 3mV. Note the peak to peak value of output voltage V<sub>o1</sub> and V<sub>o2</sub>. Calculate the voltage gain of each stage.

For stage-1,

$A_{V1} = \frac{V_{O1}}{V_{..}}$

$A_{V2} = \frac{V_{O2}}{V_{O1}}$  For stage-2,

And overall voltage gain is,

- $A_V = A_{V1} \times A_{V2}$

- 4) Vary the frequency of the input signal from 30 Hz to 500 KHz in appropriate steps, maintain the V<sub>i1</sub> constant at 2mV and note the output voltages in each step.

- 5) Calculate the gains  $A_{V1}$ ,  $A_{V2}$ , and  $A_V$  for each value of frequency. Plot a graph between gain and frequency for each stage and the overall stage

- 6) Calculate bandwidth of each stage and the overall stage from the graph.

## **Observations:**

DC conditions:

For stage-1,  $V_{BE1} = \dots$

For stage-2,  $V_{BE2} = \dots$  $I_{B2} = \dots$

$I_{B1} = \dots$

| $V_{CE1} = \dots$  |  |

|--------------------|--|

| $I_{C1} = \dots$   |  |

| V <sub>CE2</sub> = |  |

| I <sub>C2</sub> =  |  |

Frequency Response:

| Sl.No. | Frequency | V <sub>i1</sub> | V <sub>01</sub> | V <sub>O2</sub> (V) | $A_{V1} = \frac{V_{O1}}{V_{i1}}$ | $A_{V2} = \frac{V_{O2}}{V_{O1}}$ | $A_V = A_{V1} \times A_{V2}$ |

|--------|-----------|-----------------|-----------------|---------------------|----------------------------------|----------------------------------|------------------------------|

|        |           | (mV)            | (mV)            |                     | $V_{i1}$                         | $V_{o1}$                         |                              |

|        |           |                 |                 |                     |                                  |                                  |                              |

|        |           |                 |                 |                     |                                  |                                  |                              |

|        |           |                 |                 |                     |                                  |                                  |                              |

|        |           |                 |                 |                     |                                  |                                  |                              |

|        |           |                 |                 |                     |                                  |                                  |                              |

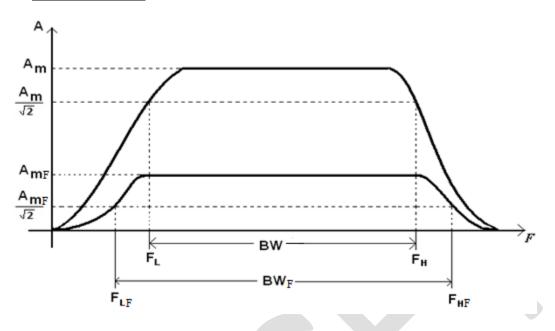

## **Expected graph:**

Fig(3) frequency response of Two stage RC Coupled CE BJT Amplifier

## **Result:**

- 1) The frequency response of individual and overall stages is plotted.

- 2) Mid frequency gains are,

| A —           | Λ —                       | A _        |

|---------------|---------------------------|------------|

| $A_{Vm1} -$   | $A_{Vm2} -$               | $A_{Vm} -$ |

| <b>1 v</b> m1 | <b>1 v</b> m <sub>2</sub> |            |

3) Bandwidths are,

| BW <sub>1</sub> = | $BW_2 =$ | BW = |

|-------------------|----------|------|

|-------------------|----------|------|

4) It is observed that cascading in amplifiers increases the voltage gain but decreases the bandwidth.

## **EXPERIMENT NO: 4**

## TWO STAGE R-C COUPLED CS JFET AMPLIFIER

#### Aim:

- 1. To design a two stage R-C coupled Common Source JFET amplifier and plot its frequency response.

- 2. To see the effect of cascading upon gain and bandwidth

#### **Components:**

| Name                                                              | Quantity   |

|-------------------------------------------------------------------|------------|

| JFET BFW 11                                                       | 2          |

| Resistor 4.7K $\Omega$ , 12K $\Omega$ , 1K $\Omega$ , 1M $\Omega$ | 2, 1, 2, 2 |

| Capacitor 1µF, 10µF, 1KPF                                         | 3,2,1      |

### **Equipment:**

| Name               | Range     | Quantity |

|--------------------|-----------|----------|

| Bread Board        |           | 1        |

| Dual power supply  | 0-30V     | 1        |

| CRO                | (0-20)MHz | 1        |

| Function Generator | (0-1)MHz  | 1        |

| Connecting Wires   |           |          |

### **Specifications:**

### For FET BFW11:

Gate Source Voltage  $V_{GS} = -30V$

Forward Gain Current I<sub>GF</sub> = 10mA

Maximum Power Dissipation  $P_D = 300 \text{mW}$

### Theory:

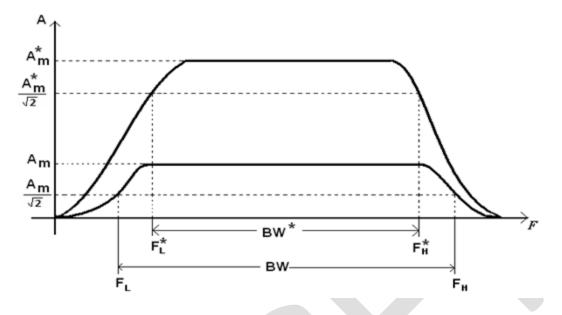

Cascading in amplifiers is a process of connecting the output of one amplifier to the input of the next and so on so forth. Cascading is used to increase the gain of the amplifiers and also to get desired values of input and output impedances.

In a multistage amplifier the overall voltage gain is the product of individual voltage gains. But the bandwidth of a multistage amplifier is always smaller than the bandwidth of individual stages.

## **Design:**

Design a two stage FET amplifier to provide an overall gain of 100, lower cutoff frequency of 75 Hz and 55 KHz. Use FET BFW10 for which  $g_m = 3 \text{ mS}$ ,  $r_d = 20 \text{ K}\Omega$ ,  $I_{DSS} = 14 \text{ mA}$ , and  $V_P = -4 \text{ V}$ . The DC conditions are as follows.  $I_D = 2.5 \text{ mA}$ ,  $V_{DS} = 10 \text{ V}$  and  $V_{DD} = 24 \text{ V}$ .

SOL:

Using

$$I_{D} = I_{DSS} \times \left(1 - \frac{V_{GS}}{V_{P}}\right)^{2}$$

$$\Rightarrow V_{GS} = V_{P} \times \left(1 - \sqrt{\frac{I_{D}}{I_{DSS}}}\right) = -2.3V$$

Assume that  $R_g = 1M\Omega$

Apply KVL to input loop:

$$-I_G \times R_g + V_{GS} + I_D \times R_S = 0$$

But  $I_G = 0$ .

$$\Rightarrow R_{S} = \frac{-V_{GS}}{I_{D}} = 0.92K\Omega \cong 1K\Omega$$

Apply KVL to the output loop:

$$-V_{DD} + I_D \times R_D + V_{DS} + I_D \times R_S = 0$$

$$\Rightarrow R_D = 5K\Omega \cong 4.7K\Omega$$

For stage-1: Gain,

$$A_{V1} = -g_m \times \left(\frac{r_d \times R_{L1}}{r_d + R_{L1}}\right) = -11.37$$

Hence the gain for second stage is given by,

$$A_{V2} = \frac{A_V}{A_{V1}} = -8.8$$

Again,

$$A_{V2} = -g_m \times \left(\frac{r_d \times R_{L2}}{r_d + R_{L2}}\right) \Longrightarrow R_{L2} = 3.44K\Omega$$

$$\Longrightarrow R_L = 12K\Omega$$

**Design of capacitors**:

Given

$$f_L^* = 75Hz$$

And individual cutoff frequency is

$$f_{L} = f_{L}^{*} \times \sqrt{2^{\frac{l}{n}} - 1}$$

$$\Rightarrow f_{L} = 48.3 Hz$$

$$C_{S} = \frac{g_{m}}{2\pi f_{L}} = 10 \mu F$$

Now,

Overall higher cutoff frequency is given as 55KHz. The higher cutoff frequency for first stage will be very high in comparison with that for the second stage. Therefore the overall higher cutoff frequency will be equal to that of the second stage.

$$\therefore f_{H2} = f_H^* = 55 KHz$$

Now,

$$C_{sh} = \frac{1}{2\pi R_{L2}^{"} f_{H2}} = 1nF = 1KPF$$

## Circuit diagram:

Fig(2)- Two stage RC Coupled CS JFET Amplifier

## **Procedure:**

- 1) Connect the circuit as shown in figure1.

- 2) Note the DC conditions i.e, the values of base, collector currents and base to emitter, collector to emitter voltages for each stage.

3) Connect the circuit as shown in figure 2, Adjust the input signal frequency to 1 KHz and the peak to peak value of  $V_{i1}$  to 10 mV. Note the peak to peak value of output voltage  $V_{o1}$  and  $V_{o2}$ . Calculate the voltage gain of each stage.

For stage-1,

$A_{V1} = \frac{V_{O1}}{V_{i1}}$

$A_{V2} = \frac{V_{O2}}{V_{O1}}$ For stage-2,

And overall voltage gain is,

- $A_V = A_{V1} \times A_{V2}$

- 4) Vary the frequency of the input signal from 30 Hz to 500 KHz in appropriate steps, maintain the  $V_{i1}$  constant at 2mV and note the output voltages in each step.

- 5) Calculate the gains  $A_{V1}$ ,  $A_{V2}$ , and  $A_V$  for each value of frequency. Plot a graph between gain and frequency for each stage and the overall stage

- 6) Calculate bandwidth of each stage and the overall stage from the graph.

## **Observations:**

DC conditions:

For stage-1,  $V_{GS1} = \dots$

For stage-2,  $V_{GS2} = \dots$

| $V_{DS1} = \dots$ |

|-------------------|

| $I_{D1} = \dots$  |

| $V_{DS2} = \dots$ |

| I <sub>D2</sub> = |

## Frequency Response:

| Sl.No. | Frequency | V <sub>i1</sub><br>(mV) | V <sub>01</sub><br>(mV) | V <sub>02</sub> (V) | $A_{V1} = rac{V_{O1}}{V_{i1}}$ | $A_{V2} = \frac{V_{02}}{V_{01}}$ | $A_V = A_{V1} \times A_{V2}$ |

|--------|-----------|-------------------------|-------------------------|---------------------|---------------------------------|----------------------------------|------------------------------|

|        |           |                         |                         |                     |                                 |                                  |                              |

|        |           |                         |                         |                     |                                 |                                  |                              |

## **Expected graph:**

Fig(3)- Frequency response of Two stage RC Coupled CS JFET Amplifier

### **Result:**

- 1) The frequency response of individual and overall stages is plotted.

- 2) Mid frequency gains are,

$A_{Vm1} = \dots \qquad A_{Vm2} = \dots \qquad A_{Vm} = \dots$

3) Bandwidths are,

$BW_1 = \dots BW_2 = \dots BW = \dots$

4) It is observed that cascading in amplifiers increases the voltage gain but decreases the bandwidth.

## **EXPERIMENT NO: 5**

## VOLTAGE SERIES FEEDBACK AMPLIFIER

#### <u>Aim:</u>

- 1. To plot the frequency response of a voltage series feedback amplifier

- 2. To see the effect of feed back upon gain and bandwidth,

#### **Components:**

| Name                                                                                                                  | Quantity      |

|-----------------------------------------------------------------------------------------------------------------------|---------------|

| Transistor BC547                                                                                                      | 2             |

| Resistor 100K $\Omega$ , 8.2K $\Omega$ , 820 $\Omega$ , 680 $\Omega$ , 120 $\Omega$ , 4.7K $\Omega$ , 2.2K $\Omega$ , | 2,4,1,1,1,1,1 |

| Capacitor 10µF,100µF, 1 KPF                                                                                           | 3, 2,1        |

## **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

### **Specifications:**

### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

## Theory:

Negative feedback is defined as a process of returning a part of the output signal to the input out of phase with the input signal. It reduces gain and increases bandwidth. Negative feedback is employed in amplifier circuits to improve the stability of the gain, reduce distortion and the effect of noise. It also helps in obtaining desired values of input and output resistances.

A voltage series feedback amplifier samples output voltage and returns the feedback signal to the input in series opposing. Feedback signal is a voltage signal.

$$V_f = \beta V_o$$

Voltage series feedback increases input resistance and decreases output resistance.

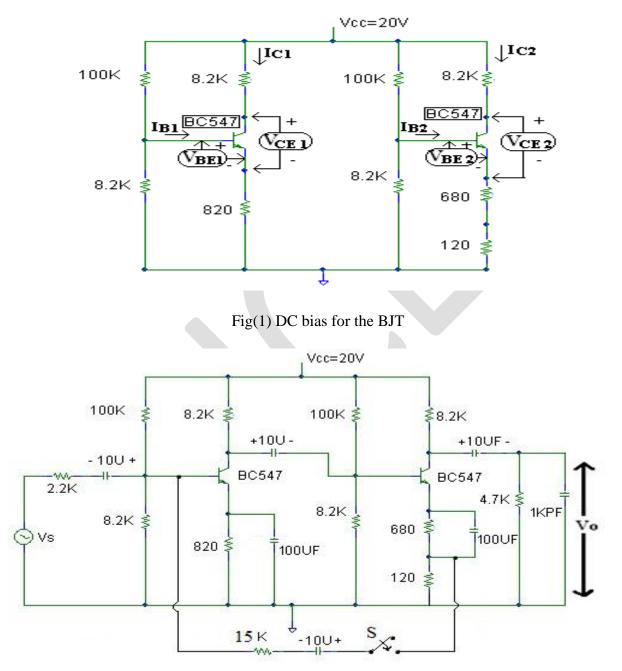

## Circuit diagram:

Fig(2) Voltage Series Feedback Amplifier

## AEC LAB MANUAL

### **Procedure:**

- 1. Connect the circuit as shown in figure 1. Note the DC conditions.

- 2. Connect the circuit as shown in figure 2. The switch must be open circuit, Then the circuit does not has feedback.

- 3. Adjust the input signal frequency to 1 KHz and the peak to peak amplitude to 3mV. Note the output voltage and calculate the gain.

- 4. Vary the frequency from 30 Hz to 500 KHz in appropriate steps and note  $V_s$  and  $V_0$  in

each case. Calculate the gain without feedback as  $A_{v} = \frac{V_{O}}{V_{S}}$

- 5. Plot a graph between gain and frequency. Calculate bandwidth from the graph.

- 6. Now connect the switch as short circuit. This will introduce voltage series feedback in the circuit. Repeat steps 3 to 5. in this case vary the frequency from 30 Hz to 2 MHz.

- 7. Compare the gain and bandwidth with and without feedback

### **Observations:**

DC conditions:-

| For stage-1, | V <sub>BE1</sub> = | V <sub>CE1</sub> = |

|--------------|--------------------|--------------------|

|              | $I_{B1} = \dots$   | I <sub>C1</sub> =  |

| For stage-2, | V <sub>BE2</sub> = | V <sub>CE2</sub> = |

|              | I <sub>B2</sub> =  | I <sub>C2</sub> =  |

Frequency Response:-

Frequency Response:

| Sl.No. Frequency $V_i$ $V_O$ $V_{Of}$ | V                       | <b>T</b> 7                    |

|---------------------------------------|-------------------------|-------------------------------|

| (mV) (V) (V)                          | $A_V = \frac{V_O}{V_i}$ | $A_{Vf} = \frac{V_{Of}}{V_i}$ |

|                                       |                         |                               |

|                                       |                         |                               |

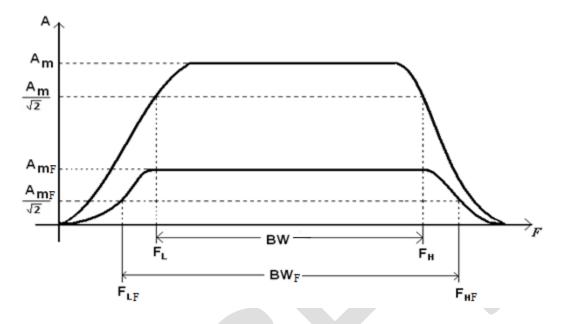

**Expected graph:**

Fig(3) Frequency response of Voltage Series Feedback Amplifier

## **Result:**

Gain without feedback = -----

### Bandwidth without feedback = ----

Gain with feedback = ------

Bandwidth with feedback = -----

## **EXPERIMENT NO: 6**

## CURRENT SHUNT FEEDBACK AMPLIFIER

#### <u>Aim:</u>

- 1. To plot the frequency response of a current shunt feedback amplifier

- 2. To see the effect of feed back upon gain and bandwidth,

#### **Components:**

| Name                                                                                                                  | Quantity      |

|-----------------------------------------------------------------------------------------------------------------------|---------------|

| Transistor BC547                                                                                                      | 2             |

| Resistor 100K $\Omega$ , 8.2K $\Omega$ , 820 $\Omega$ , 680 $\Omega$ , 120 $\Omega$ , 4.7K $\Omega$ , 2.2K $\Omega$ , | 2,4,1,1,1,1,1 |

| Capacitor 10µF,100µF, 1 KPF                                                                                           | 3, 2,1        |

## **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

### **Specifications:**

### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

## Theory:

Negative feedback is defined as a process of returning a part of the output signal to the input out of phase with the input signal. It reduces gain and increases bandwidth. Negative feedback is employed in amplifier circuits to improve the stability of the gain, reduce distortion and the effect of noise. It also helps in obtaining desired values of input and output resistances.

A current shunt feedback amplifier samples output current and returns the feedback signal to the input in shunt. Feedback signal is a voltage signal.

$$I_f = \beta I_L$$

Current shunt feedback increases output resistance and decreases input resistance.

## Circuit diagram:

Fig(2) Current Shunt Feedback Amplifier

## AEC LAB MANUAL

## **Procedure:**

- 1. Connect the circuit as shown in figure 1. Note the DC conditions.

- 2. Connect the circuit as shown in figure 2. The switch must be open circuit, Then the circuit does not has feedback.

- 3. Adjust the input signal frequency to 1 KHz and the peak to peak amplitude to 3mV. Note the output voltage and calculate the gain.

- 4. Vary the frequency from 30 Hz to 500 KHz in appropriate steps and note  $V_s$  and  $V_0$  in

each case. Calculate the gain without feedback as  $A_{v} = \frac{V_{o}}{V_{s}}$

- 5. Plot a graph between gain and frequency. Calculate bandwidth from the graph.

- 6. Now connect the switch as short circuit. This will introduce current shunt feedback in the circuit. Repeat steps 3 to 5. in this case vary the frequency from 30 Hz to 2 MHz.

- 7. Compare the gain and bandwidth with and without feedback

### **Observations:**

DC conditions:

For stage-1,  $V_{BE1} = \dots$

I<sub>B1</sub> = .....

For stage-2,

$V_{BE2} = \dots$  $I_{B2} = \dots$   $V_{CE1} = \dots$   $I_{C1} = \dots$   $V_{CE2} = \dots$  $I_{C2} = \dots$

### Frequency Response:

| Sl.No. | Frequency | V <sub>i</sub><br>(mV) | V <sub>0</sub><br>(V) | V <sub>Of</sub><br>(V) | $A_V = \frac{V_O}{V_i}$ | $A_{Vf} = \frac{V_{Of}}{V_i}$ |

|--------|-----------|------------------------|-----------------------|------------------------|-------------------------|-------------------------------|

|        |           |                        |                       |                        |                         |                               |

|        |           |                        |                       |                        |                         |                               |

## **Expected graph:**

Fig(3) frequency response of Current Shunt Feedback Amplifier

## **Result:**

- Gain without feedback = -----

- Bandwidth without feedback = ------

Gain with feedback = -----

Bandwidth with feedback = ------

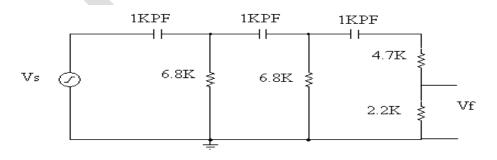

## **EXPERIMENT NO: 7**

## **RC PHASE-SHIFT OSCILLATOR**

### <u>Aim:</u>

To design and study the operation of RC Phase-shift Oscillator using BJT and verify Barkhausen's criterion.

#### **Components:**

| Name                                                                           | Quantity    |

|--------------------------------------------------------------------------------|-------------|

| Transistor BC547                                                               | 1           |

| Resistor 74K $\Omega$ , 15K $\Omega$ , 4.7K $\Omega$ , 1K $\Omega$ , 6.8K,2.2K | 1,1,2,1,2,1 |

| Capacitor 10µF,100µF, 1 KPF                                                    | 2, 1,3      |

## **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

### **Specifications:**

### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

### Theory:-

An oscillator is an electronic circuit that provides an AC output without using any AC input. All Sinusoidal oscillator circuits use the concept of positive feedback to produce oscillations. An oscillator circuit must satisfy the Barkhausen's criterion of unity loop gain to produce oscillations.

The Common Emitter amplifier provides a phase shift of 180°. Additional 180° of phase shift required to satisfy the Barkhausen's criterion of phase shift is provided by the RC phase-shifting network. RC Phase-shift oscillator is used at Audio Frequencies.

## **Design:**

Q: Design RC Phase-shift oscillator circuit to provide oscillations at a frequency of 8 KHz. Use BJT BC547 for which  $\beta = 200$ ,  $h_{fe} = 50$ ,  $h_{ie} = 1.5$  K $\Omega$  and  $V_{BE(active)} = 0.65$ V. The biasing conditions are as follows.  $V_{CC} = 12$ V,  $I_C = 1$ mA,  $V_{CE} = 6$ V and Stability factor is S = 10. Use  $R_C = 4.7$ K $\Omega$ .

## Solution:

Use,  $I_C = \beta \times I_B$

$\Rightarrow I_B = 5\mu A$

Apply KVL to the output loop:

$$-V_{CC} + I_C \times R_C + V_{CE} + I_C \times R_E = 0$$

$$\Rightarrow R_E = 1.3K\Omega$$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2} \text{ And } R_B = \frac{R_1 \times R_2}{R_1 + R_2}$$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1+\beta}{1+\frac{\beta \times R_E}{R_B + R_E}}$$

$$\implies R_B = 12.31K\Omega$$

Apply KVL to the input loop, then

$$-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$$

$$\Rightarrow V_{E} - 2.01 \text{ V}$$

Divide  $R_B$  with  $V_B$ :

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_B} = 73.5 K\Omega$$

Also,

$$R_B = \frac{R_1 \times R_2}{R_1 + R_2} \implies R_2 = 14.8 K\Omega$$

$$f_o = \frac{1}{2\pi \times RC\sqrt{6+4K}}$$

We know that

$$R$$

where  $K = \frac{K_C}{R}$

Assume that  $R = 6.8K\Omega$ . Then C = 1KPF.

Also

$$R_3 + h_{ie} = R \implies R_3 = 4.7 K\Omega$$

## Circuit diagram:-

Fig (1): RC Phase shift oscillator

Fig (2): Amplifier Circuit diagram

## Fig (3): Feedback network

#### **Procedure:-**

#### **Part-I: Study of operation**

- 1) Connect the self bias circuit and check the DC conditions.

- 2) Connect other components of the oscillator circuit as shown in figure. Observe the output voltage waveform on CRO screen. Note down its peak to peak amplitude and frequency.

## Part-II: Verification of Barkhausen's criterion

- 1) Connect only the amplifier circuit and find its gain at the frequency of oscillations. Apply an input of 30mV. Also observe the phase shift between input and output voltages.

- 2) Connect only the feedback network as shown and compute the feedback factor  $\beta$  as  $\beta = \frac{V_f}{V_c}$

- 3) Compute the loop gain as  $A \times \beta$ . This product should be greater than or equal to unity.

- 4) Observe the phase shift between  $V_f$  and  $V_s$ .

- 5) Add the phase shift provided by the amplifier and feedback network. The sum should be equal to 360°.

#### **Observations: -**

Draw the output waveform; mark its peak-to-peak amplitude and time period.

#### **Result:-**

Frequency of oscillations, f<sub>o</sub> = -----

Peak to peak amplitude of output = -----

Loop gain = -----

Phase shift = -----

Hence Barkhausen's criterion is satisfied.

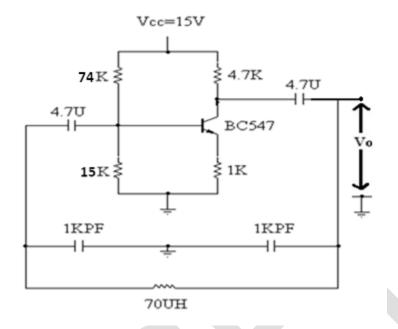

## **EXPERIMENT NO: 8**

## **COLPITTS OSCILLATOR**

#### Aim:

To design and study the operation of colpitts Oscillator using BJT and determine the frequency of oscillation.

#### **Components:**

| Name                                                                  | Quantity |

|-----------------------------------------------------------------------|----------|

| Transistor BC547                                                      | 1        |

| Resistor 74K $\Omega$ , 15 K $\Omega$ , 4.7K $\Omega$ , 1K $\Omega$ , | 1,1,1,1  |

| Capacitor 4.7µF, 1 KPF                                                | 2, 1     |

| Inductor 70 µH                                                        | 1        |

#### **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

## **Specifications:**

#### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

#### Theory:-

An oscillator is an electronic circuit that provides an AC output without using any AC input. All Sinusoidal oscillator circuits use the concept of positive feedback to produce oscillations. An

oscillator circuit must satisfy the Barkhausen's criterion of unity loop gain to produce oscillations.

Colpitt's oscillator is a popular LC Oscillator circuit used at Radio Frequencies.

## Design:

Q: Design Colpitt's oscillator circuit to provide oscillations at a frequency of 850 KHz. Use BJT BC547 for which  $\beta = 200$ ,  $h_{fe} = 50$ ,  $h_{ie} = 1.5 \text{ K}\Omega$  and  $V_{BE(active)} = 0.65 \text{ V}$ . The biasing conditions are as follows.  $V_{CC} = 12 \text{ V}$ ,  $I_C = 1 \text{ mA}$ ,  $V_{CE} = 6 \text{ V}$  and Stability factor is S = 10. Use  $R_C = 4.7 \text{K}\Omega$ .

## Solution:

Use,  $I_c = \beta \times I_B$

$$\Rightarrow I_B = 5\mu A$$

Apply KVL to the output loop:

$$-V_{CC} + I_C \times R_C + V_{CE} + I_C \times R_E = 0$$

$$\Rightarrow R_E = 1.3K\Omega$$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

And  $R_B = \frac{R_1 \times R_2}{R_1 + R_2}$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1+\beta}{1+\frac{\beta \times R_E}{R_B+R_E}}$$

$$\Rightarrow R_B = 12.31K\Omega$$

Circuit diagram:-

Apply KVL to the input loop, then  $-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$   $\Rightarrow V_B = 2.01 \text{ V}$

Divide  $R_B$  with  $V_B$ :

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_B} = 73.5 K\Omega$$

Also,

$$R_B = \frac{R_1 \times R_2}{R_1 + R_2} \implies R_2 = 14.8K\Omega$$

$$f_o = \frac{1}{2\pi} \times \sqrt{\frac{1}{L}(\frac{1}{C_1} + \frac{1}{C_2})}$$

We know that

Assume that  $C_1 = C_2 = 1KPF$ . Then  $L = 70 \mu H$

Fig (1): Colpitts Oscillator

## Procedure:-

- 1) Connect the self bias circuit and check the DC conditions.

- 2) Connect other components of the oscillator circuit as shown in figure 1. Adjust the capacitance to 800 PF.

- 3) Observe the output voltage waveform on CRO screen. Note down its peak to peak amplitude and frequency.

- 4) Vary the inductance in appropriate steps and record the frequency in each case.

- 5) Calculate the frequency theoretically and record it in the table. Compare the theoretical and practical values.

#### **Observations:-**

#### DC conditions:-

| V <sub>BE</sub> = | V <sub>CE</sub> = |

|-------------------|-------------------|

| I <sub>B</sub> =  | I <sub>C</sub> =  |

|                   |                   |

| Sl. No. | Inductance | Frequency              | Frequency                                                                       |

|---------|------------|------------------------|---------------------------------------------------------------------------------|

|         | (µH)       | (Practically)<br>(KHz) | $f_o = \frac{1}{2\pi} \times \sqrt{\frac{1}{L}(\frac{1}{C_1} + \frac{1}{C_2})}$ |

|         |            |                        |                                                                                 |

# Result:-

Colpitts oscillator circuit is designed for the given specifications and its operation is studied.

# **EXPERIMENT NO: 9**

# HARTLEY OSCILLATOR

# <u>Aim:</u>

To design and study the operation of Hartley Oscillator using BJT and determine the frequency of oscillation.

# **Components:**

| Name                                                                  | Quantity |

|-----------------------------------------------------------------------|----------|

| Transistor BC547                                                      | 1        |

| Resistor 74K $\Omega$ , 15 K $\Omega$ , 4.7K $\Omega$ , 1K $\Omega$ , | 1,1,1,1  |

| Capacitor 4.7µF, 100 PF                                               | 2, 1     |

| Inductor 70 µH                                                        | 2        |

## **Equipment:**

| Name                 | Range | Quantity |

|----------------------|-------|----------|

| Bread Board          |       | 1        |

| Dual DC power supply | 0-30V | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1 |

|------------------------------|--------------------------|---|

| CRO                          | (0-20)MHz                | 1 |

| CRO probes, Connecting Wires |                          |   |

## **Specifications:**

#### For Transistor BC 547:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

## Theory:-

An oscillator is an electronic circuit that provides an AC output without using any AC input. All Sinusoidal oscillator circuits use the concept of positive feedback to produce oscillations. An oscillator circuit must satisfy the Barkhausen's criterion of unity loop gain to produce oscillations.

Hartley's oscillator is a popular LC Oscillator circuit used at Radio Frequencies.

## **Design:**

Q: Design Hartley's oscillator circuit to provide oscillations at a frequency of 850 KHz. Use BJT BC547 for which  $\beta = 200$ ,  $h_{fe} = 50$ ,  $h_{ie} = 1.5 \text{ K}\Omega$  and  $V_{BE(active)} = 0.65 \text{V}$ . The biasing conditions are as follows. $V_{CC} = 12 \text{V}$ ,  $I_C = 1 \text{mA}$ ,  $V_{CE} = 6 \text{V}$  and Stability factor is S = 10. Use  $R_C = 4.7 \text{K}\Omega$ . Solution:

Use,  $I_c = \beta \times I_B$

$$\Rightarrow I_{P} = 5 \mu A$$

Apply KVL to the output loop:

$$-V_{CC} + I_C \times R_C + V_{CE} + I_C \times R_E = 0$$

$$\Rightarrow R_E = 1.3K\Omega$$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

And  $R_B = \frac{R_1 \times R_2}{R_1 + R_2}$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1 + \beta}{1 + \frac{\beta \times R_E}{R_B + R_E}}$$

$$\implies R_B = 12.31K\Omega$$

Apply KVL to the input loop, then

$$-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$$

$$\Rightarrow V_B = 2.01 \,\mathrm{V}$$

Divide R<sub>B</sub> with V<sub>B</sub>:

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_B} = 73.5 K\Omega$$

Also,

$$R_B = \frac{R_1 \times R_2}{R_1 + R_2} \implies R_2 = 14.8K\Omega$$

$f_g = \frac{1}{1 + R_2}$

$2\pi\sqrt{(L_1+L_2+2M)C}$

Assume that  $L_1 = L_2 = 70 \mu H$  and  $M = 45 \mu H$ . Then C = 100 pF.

**Circuit diagram:-**

We know that

Fig (1): Hartley's Oscillator

# **Procedure:-**

- 1) Connect the self bias circuit and check the DC conditions.

- 2) Connect other components of the oscillator circuit as shown in figure. Adjust the capacitance to 800 PF.

- 3) Observe the output voltage waveform on CRO screen. Note down its peak to peak amplitude and frequency.

- 4) Vary the capacitance in appropriate steps and record the frequency in each case.

- 5) Calculate the frequency theoretically also and record it in the table. Compare the theoretical and practical values.

#### **Observations:-**

DC conditions:-

$V_{BE} = \dots$

$V_{CE} = \dots$

$I_B = \dots$

$I_C = \dots$

| Sl. No. | Capacitance   | Frequency              | Frequency                                      |

|---------|---------------|------------------------|------------------------------------------------|

|         | ( <b>PF</b> ) | (Practically)<br>(MHz) | $f_o = \frac{1}{2\pi\sqrt{(L_1 + L_2 + 2M)C}}$ |

|         |               |                        |                                                |

## **Result:-**

Hartley oscillator circuit is designed for the given specifications and its operation is studied.

## **EXPERIMENT NO: 10**

## SINGLE TUNED AMPLIFIER

## Aim:-

To design and plot the frequency response of a single tuned amplifier.

## **Components:**

| Name                                                                 | Quantity |

|----------------------------------------------------------------------|----------|

| Transistor BF194                                                     | 1        |

| Resistor 94K $\Omega$ , 68K $\Omega$ , 3.9K $\Omega$ , 2.2K $\Omega$ | 1,1,1,1  |

| Capacitor 10μF,100μF, 3.18 ηF                                        | 2, 1,1   |

| Inductor 39 µH                                                       | 1        |

# **Equipment:**

| Name Range Quantity |

|---------------------|

|---------------------|

# DEPARTMENT OF ECE

| Bread Board                  |                          | 1 |

|------------------------------|--------------------------|---|

| Dual DC power supply         | 0-30V                    | 1 |

| Function Generator           | (0-1)MHz                 | 1 |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1 |

| CRO                          | (0-20)MHz                | 1 |

| CRO probes, Connecting Wires |                          |   |

## **Specifications:**

#### For Transistor BF 194:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>0</sup>C

- $h_{fe} = 110 220$

#### Theory:-

Tuned amplifier circuit uses parallel LC resonant circuit as the load impedance, They have a very narrow bandwidth, hence they select a particular frequency and rejects other, they are used in radio receivers.

A single tuned amplifier consists of only one LC section as a load.

## Design: -

Design a single tuned amplifier to provide a gain of 100 at a frequency of 455 KHZ and provide a bandwidth of 20 KHZ. Use transistor BF194 for which  $\beta = 90$ ,  $g_m = 40mS$ . The biasing conditions are as follows.  $V_{CC} = 12V$ ,  $V_{CE} = 8V$ , IC = 1mA and S = 10.

#### Sol:

Use,  $I_c = \beta \times I_B$ ,  $\Rightarrow I_B = 11.11 \mu A$

Apply KVL to the output loop:

$$-V_{CC} + V_{CE} + I_C \times R_E = 0$$

$$\Rightarrow R_E = 4K\Omega \cong 3.9K\Omega$$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

And  $R_B = \frac{R_1 \times R_2}{R_1 + R_2}$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1 + \beta}{1 + \frac{\beta \times R_E}{R_B + R_E}}$$

$$\implies R_B = 39.43K\Omega$$

Apply KVL to the input loop, then

$$-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$$

$$\Rightarrow V_B = 5V$$

Divide R<sub>B</sub> with V<sub>B</sub>:

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_R} = 94.63 K\Omega$$

Also,

$$R_B = \frac{R_1 \times R_2}{R_1 \div R_2} \implies R_2 = 68K\Omega$$

ł

Design of tuned circuit:-

Effective quality factor is given by

$$Q_e = \frac{f_o}{BW} = 22.75$$

We know that the gain of a single tuned amplifier at resonant frequency is given by,

$$|A_{res}| = g_m \varpi_o L Q_e$$

$$\Rightarrow L = 38.44 \mu H$$

Also the resonant frequency of the single tuned amplifier is given by,

$$\varpi_o = \frac{1}{\sqrt{LC}}$$

$$\Rightarrow C = \frac{1}{\varpi_o^2 \times L} = 3.183 nF$$

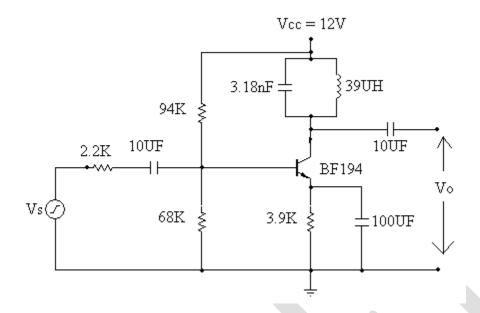

**Circuit diagram:-**

Fig (1): Single tuned amplifier

## **Procedure:-**

- 1) Connect the self bias circuit and check the DC conditions.

- 2) Connect the other components and set the generator frequency at 455KHZ. Adjust the peak to peak amplitude of the input voltage to 30mV. Observe the output voltage waveform on the CRO screen and note the peak to peak value of the output voltage. Calculate the gain.

- 3) Vary the frequency from 400 to 600KHZ in appropriate steps.

- 4) Calculate the gain for each frequency.

- 5) Plot a graph between gain and frequency. Calculate bandwidth from the graph.

#### **Observations:-**

#### DC conditions:-

| $V_{BE} = \dots$ | $V_{CE} = \dots$ |

|------------------|------------------|

| $I_B = \dots$    | I <sub>C</sub> = |

## Frequency Response:-

| Sl. No. | Frequency | V <sub>i</sub> (mV) | V <sub>o</sub> (V) | $Gain = \frac{Vo}{Vi}$ |

|---------|-----------|---------------------|--------------------|------------------------|

|         |           |                     |                    |                        |

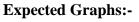

# **Expected Graph:-**

Fig (2): Frequency response of single tuned amplifier

## **Result:-**

Resonant frequency = -----

Gain at resonance = -----

Bandwidth = -----

## **EXPERIMENT NO: 11**

## **DOUBLE TUNED AMPLIFIER**

#### Aim:-

To design and plot the frequency response of a double tuned amplifier.

#### **Components:**

| Name                                                                 | Quantity |

|----------------------------------------------------------------------|----------|

| Transistor BF194                                                     | 1        |

| Resistor 94K $\Omega$ , 68K $\Omega$ , 3.9K $\Omega$ , 2.2K $\Omega$ | 1,1,1,1  |

| Capacitor 10µF,100µF, Capacitance box                                | 2, 1,1   |

| Inductance box                                                       | 1        |

#### Equipment:

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Dual DC power supply         | 0-30V                    | 1        |

| Function Generator           | (0-1)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

## **Specifications:**

#### For Transistor BF 194:

- Max Collector Current= 0.1A

- $V_{ceo}$  max= 50V

- $V_{EB0} = 6V$

- $V_{CB0} = 50V$

- Collector power dissipation = 500mW

- Temperature Range = -65 to +150 <sup>o</sup>C

- $h_{fe} = 110 220$

#### Theory:-

Tuned amplifier circuit uses parallel LC resonant circuit as the load impedance, They have a very narrow bandwidth, hence they select a particular frequency and rejects other, they are used in radio receivers.

A double tuned amplifier consists of two LC sections as a load.

## **Design:-**

Design a double tuned amplifier to provide maximum gain at a frequency of 350KHz. Use transistor BF194 for which  $\beta = 90$ ,  $g_m = 40mS$ .

The biasing conditions are as follows.  $V_{CC} = 12V$ ,  $V_{CE} = 8V$ , IC = 1mA and S = 10.

## Sol:-

Use,  $I_C = \beta \times I_B$ ,  $\Rightarrow I_B = 11.11 \mu A$ Apply KVL to the output loop:  $-V_{CC} + V_{CE} + I_C \times R_E = 0$

$$\Rightarrow R_F = 4K\Omega \cong 3.9K\Omega$$

Apply Thevenin's theorem to the base circuit, then

$$V_B = \frac{V_{CC} \times R_2}{R_1 + R_2}$$

And  $R_B = \frac{R_1 \times R_2}{R_1 + R_2}$

We know that the stability factor for a self bias circuit is given by,

$$S = \frac{1 + \beta}{1 + \frac{\beta \times R_E}{R_B + R_E}}$$

$$\Rightarrow R_B = 39.43K\Omega$$

Design of tuned circuit:-

An Intermediate Frequency Transformer with a centre frequency of 350 KHz is used.

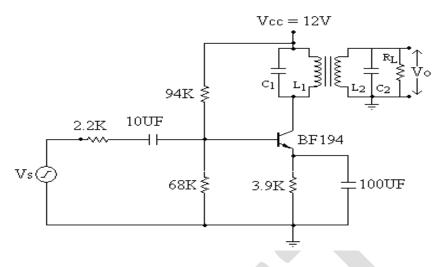

## Circuit diagram:-

Apply KVL to the input loop, then

$$-V_B + I_B \times R_B + V_{BE} - I_E \times R_E = 0$$

$$\implies V_B = 5V$$

Divide R<sub>B</sub> with V<sub>B</sub>:

$$\Rightarrow R_1 = \frac{V_{CC} \times R_B}{V_R} = 94.63 K\Omega$$

$$R_B = \frac{R_1 \times R_2}{R_1 \div R_2} \implies R_2 = 68K\Omega$$

Fig (1): Double tuned amplifier

### **Procedure:-**

- 1) Connect the self bias circuit and check the DC conditions.

- 2) Connect the other components and set the generator frequency at 350KHZ. Adjust the peak to peak amplitude of the input voltage to 30mV. Observe the output voltage waveform on the CRO screen and note the peak to peak value of the output voltage. Calculate the gain.

- 3) Vary the frequency from 250 to 500KHZ in steps of 10KHz and record  $V_i$ ,  $V_o$  in every step.

- 4) Calculate the gain for each frequency.

- 5) Plot a graph between gain and frequency. Calculate bandwidth from the graph.

#### **Observations:-**

#### DC conditions:-

| V <sub>BE</sub> = | V <sub>CE</sub> = |

|-------------------|-------------------|

| I <sub>B</sub> =  | I <sub>C</sub> =  |

#### Frequency Response:-

| Sl. No. | Frequency | V <sub>i</sub> (mV) | $V_{o}(V)$ | $Gain = \frac{Vo}{Vi}$ |

|---------|-----------|---------------------|------------|------------------------|

|         |           |                     |            |                        |

|         |           |                     |            |                        |

Expected Graph:-

Fig (2): Frequency response of double tuned amplifier

## **Result:-**

Resonant frequency = -----

Gain at resonance = -----

Bandwidth = -----

# **Experiment no: 12**

# **Constant K Low Pass Filter.**

### Aim:-

1) To design a T-section constant K Low Pass Filter with a cut-off frequency of 2 KHz and a characteristic load impedance of  $600\Omega$ .

2) To obtain the output characteristics of the above filter.

#### **Components:**

| Name                 | Quantity |

|----------------------|----------|

| Resistor $600\Omega$ | 1        |

| Capacitance box      | 1        |

| Inductance box       | 2        |

#### **Equipment:**

| Name                         | Range                    | Quantity |

|------------------------------|--------------------------|----------|

| Bread Board                  |                          | 1        |

| Function Generator           | (0-2)MHz                 | 1        |

| Digital Ammeter, Voltmeter   | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz                | 1        |

| CRO probes, Connecting Wires |                          |          |

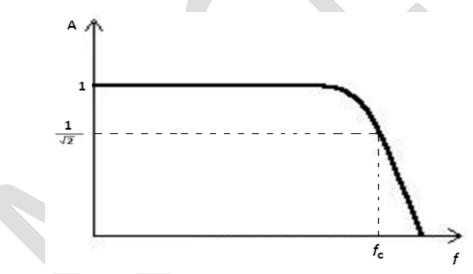

## Theory:-

Low pass filter is a circuit which passes low frequency signals and attenuates high frequency signals,

The frequency at which the gain is 70% of the maximum value is called as cut off frequency.

## Design:-

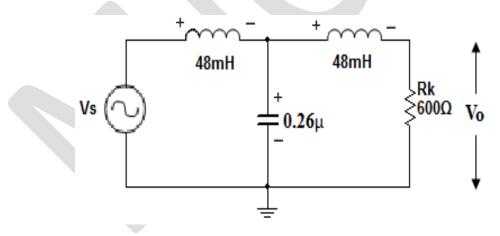

We know that the cut off frequency is given by,

$$f_C = \frac{1}{\pi \sqrt{LC}}$$

$$R_{K} = \sqrt{\frac{L}{C}}$$

and the characteristic load impedance is,

then the design equations for L and C will be

$$L = \frac{R_{\kappa}}{\pi f_{c}} = \frac{600}{\pi \times 2000} = 48mE$$

$$C = \frac{1}{\pi R_{\rm K} f_{\rm C}} = \frac{1}{\pi \times 600 \times 2000} = 0.26 \,\mu F$$

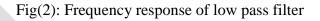

**Circuit Diagram:-**

Fig (1): Low pass filter

# Procedure:-

- 1) Connect the components as shown in the circuit diagram.

- 2) Adjust  $V_i = 4V$  (peak-to-peak) and keep it constant throughout the experiment.

3) Vary the input frequency from 100 Hz to 20 Khz in steps of 200 Hz and note down the peak-to-peak voltage across  $R_L$  i.e.,  $V_O$ .

Note: Take more readings between 1.8KHz and 2.2KHz.

- 4) Plot the variation of Gain Versus frequency

- 5) From the graph find out  $f_c$ .

## **Observations:-**

| Sl.<br>No. | Frequency<br>(Hz) | V <sub>i</sub><br>(Volt) | V <sub>O</sub><br>(Volt) | $\mathbf{A} = \frac{v_o}{v_i}$ | $\alpha = \ln\!\left(\frac{V_i}{V_o}\right)$ |

|------------|-------------------|--------------------------|--------------------------|--------------------------------|----------------------------------------------|

|            |                   |                          |                          |                                |                                              |

| _ |  |      |  |

|---|--|------|--|

|   |  |      |  |

|   |  |      |  |

|   |  |      |  |

| _ |  | <br> |  |

|   |  |      |  |

|   |  |      |  |

|   |  |      |  |

|   |  |      |  |

**Results:-**

From the attenuation characteristics curve,

$f_C = \dots Hz$

# **Experiment no: 13**

## m-Derived High Pass Filter

### Aim:-

1) To design an m-derived high pass T-section filter with a cut-off frequency of 1.2 KHz, characteristic load impedance of 600  $\Omega$  and  $f_{\infty} = 1.1 KHz$

2) To obtain output characteristics of the above filter.

#### **Components:**

| Name                 | Quantity |

|----------------------|----------|

| Resistor $600\Omega$ | 1        |

| Capacitance box      | 3        |

| Inductance box       | 1        |

#### **Equipment:**

| Name                       | Range                    | Quantity |

|----------------------------|--------------------------|----------|

| Bread Board                |                          | 1        |

| Function Generator         | (0-2)MHz                 | 1        |

| Digital Ammeter, Voltmeter | [0-200µA/200mA], [0-20V] | 1        |

| CRO                          | (0-20)MHz | 1 |

|------------------------------|-----------|---|

| CRO probes, Connecting Wires |           |   |

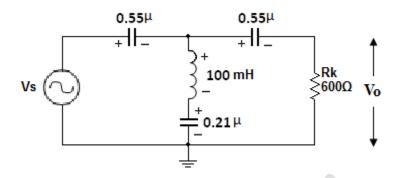

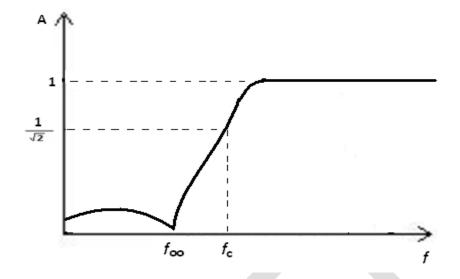

## **Theory:-**

High pass filter is a circuit which passes high frequency signals and attenuates low frequency signals,

The frequency at which the gain is 70% of the maximum value is called as cut off frequency.

m-derived filters have a very sharp cut off frequency

## Design:-

a) Design of prototype High Pass T-section

$$L = \frac{R_o}{4\pi f_c} = \frac{600}{4\pi \times 1200} = 39.78 mH$$

$$C = \frac{1}{4\pi R_o f_c} = \frac{1}{4\pi \times 600 \times 1200} = 0.11 \mu F$$

Value of m for m-derived section to give infinite attenuation at 1100 Hz is given by,

$$m = \sqrt{1 - \left(\frac{f_{\infty}}{f_C}\right)^2} = \sqrt{1 - \left(\frac{1100}{1200}\right)^2} = 0.4$$

b) for the m-derived T-section

2C0.22  $= 0.55 \,\mu F$ 0.4Each series arm

$$= \frac{L}{m} = \frac{39.78}{0.4} = 99.45mH$$

Shu

And,

$$\frac{4mC}{1-m^2} = \frac{4 \times 0.4 \times 0.11}{1-(0.4)^2} = 0.21 \mu F$$

**Circuit Diagram:-**

Fig (1): High pass filter

## Procedure:-

- 1) Connect the components as shown in the circuit diagram.

- 2) Adjust  $V_i = 4V$  (peak-to-peak) and keep it constant throughout the experiment.

- 3) Vary the input frequency from 100 Hz to 20 Khz in steps of 200 Hz and note down the peak-to-peak voltage across  $R_L$  i.e.,  $V_O$ .

Note: Take more readings between 1.1KHz and 1.2KHz.

- 4) Plot the variation of Gain Versus frequency